Рейтинг: 4.7/5.0 (1915 проголосовавших)

Рейтинг: 4.7/5.0 (1915 проголосовавших)Категория: Инструкции

Внимание! С 1 по 8 октября наш магазин уходит на каникулы. Заказы, оплаченные после 20:00

30 сентября, будут отправлены после 8 октября. Ваши сообщения и вопросы, отправленные в этот период, будут рассмотрены

после 8 октября.

При оплате до пятницы 20:00 заказы с почтовой доставкой будут отправлены в течение суток, со способами доставки Самовывоз и Курьер - переданы в службу доставки 2 октября.

Ваша корзина пуста

Мы находимся в

Ростовской области

8-800-200-20-27

Звонок из любой точки России бесплатный

Звонки принимаются

с 10:00 до 20:00

Мы работаем без праздников и выходных!

Лучший интернет-магазин рукоделия 2014 года по версии читателей журнала "Формула рукоделия"

Рассылка о новинках

Внимание! Для подписки Вам необходимо включить JavaScript.

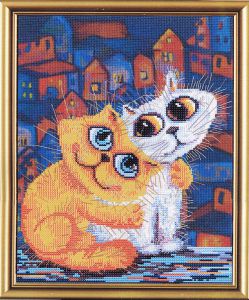

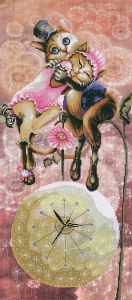

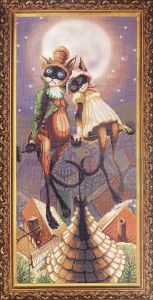

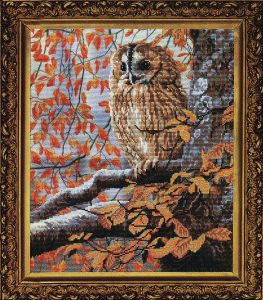

Производитель: Нова Слобода (Украина) Техника: Частичная вышивка Тип схемы: Цветная символьная схема Канва: Аида 16 Цвет канвы: Тонированная По мотивам Соколова Н.С. В наборе используется: мулине Фирма ниток: Avrora 120 Оформление (аксессуары): Рамка и паспарту в комплект не входят Игла: Игла Инструкция: На русском языке Кол-во цветов: 37 Размер: 35x47 см Нитки разобраны на органайзер

Похожие продукты

Арт. CP4089 (4089-CP)

Арт. CP4085 (4085-CP)

Арт. CP4093 (4093-CP)

Арт. CP4051 (4051-CP)

Арт. CP6116 (6116-CP)

Арт. CP6073 (6073-CP)

Арт. CP6071 (6071-CP)

Арт. HHK3129 (3129-HHK)

Информация Актуально Способы оплаты© Магазин «Руковечка» 2015 — 2016

Привет!

Я очень рада тебя видеть!

Давай знакомиться!

Меня зовут Руковечка. А тебя?

У меня есть секретные скидки!

Только для друзей.

Теперь мы стали друзьями!

Я пришлю тебе на Email

секретную скидочку!

Уииии!

Побежала отправлять скидку!

Здравствуйте!

Меня зовут Руковечка.

Я просто обожаю рукодельничать!

И у меня для вас есть подарочек!

Скидка 5%!

Всего один шаг

и скидка ваша!

Готово! Письмо отправлено!

Приятных покупок!

Геннадий Геннадий Мыслитель (6799), закрыт 3 года назад

решил прикупить процессор

зашел в разделхарактеристики

а там такая графа:

надор инструкций для процессора

и такие инструкции:

наборы инструкций: SSE, SSE2, SSE3, SSE4.2,

расширения AVX 2.0,

Intel Virtualization Technology (VT-x),

Intel Virtualization Technology for Directed I/O (VT-d),

Intel Trusted Execution Technology,

Аппаратное ускорение шифрования AES,

Enhanced Halt State (C1E),

Enhanced Intel Speedstep Technology,

EVP (Enhanced Virus Protection или Execute Disable Bit),

Intel vPro Technology,

Intel TSX-NI

-----

что они означают?

если можно по русски

(на вики был - результат тот же)

----

вот ссылка на процессор в магазине НИКС

http://kocha.co/drr/

Kalyan Kalyan Оракул (66507) 3 года назад

mks skm Мыслитель (8993) 3 года назад

изучай каждый параметр по отдельности если не в падлу,

тогда всё разъесниться

Юзер Честный Просветленный (31316) 3 года назад

Вы издеваетесь? Здесь места не хватит.

"на вики был - результат тот же" - тот же - это какой? читать не умеете?

Геннадий Геннадий Мыслитель (6799) 3 года назад

это я уже читал

не зги не понял

Юзер Честный Просветленный (31316) Ну, значит, Вам рано. или не надо вовсе.

rocknrolldevil mmm Гуру (3042) 3 года назад

вам оно ненужно. и вряд ли поможет. валяйте дурака дальше.

Геннадий Геннадий Мыслитель (6799) 3 года назад

111 111 Мыслитель (8115) 3 года назад

Чем больше инструкций, тем лучше.

Геннадий Геннадий Мыслитель (6799) 3 года назад

чем больше - тем дороже

а дороже - не значит качественней

111 111 Мыслитель (8115) больше не куда, это процессор не с сокращенным набором инструкций. чтобы купить макмально производительный процессор для компьютера, нужно выбрать процессор с: 1) наиболее новой архитектурой 2) максимальной частотой ядра 3) максимальным размером кэша L2/L3 4) большим набором доступных инструкций 5) минимальным технологическим процессом изготовления

Сергей Савельев Профи (698) 3 года назад

денис иванов Гуру (3633) 3 года назад

какие нафиг инструкции это технические характеристики

по приведению в транспортное положение и порядку

сопровождения специального подвижного состава

I. Общие положения

1.1. Настоящая Инструкция устанавливает порядок приведения в транспортное положение и сопровождения специального подвижного состава федерального железнодорожного транспорта (далее - машины), условия транспортирования различных машин, определяет необходимые меры, обеспечивающие сохранность транспортируемых машин и безопасность их движения на сети железных дорог Российской Федерации.

К транспортированию по железным дорогам Российской Федерации допускаются машины, конструкция которых соответствует согласованным и утвержденным в установленном порядке проектам и техническим условиям.

Настоящая Инструкция отражает конструкцию машин, находящихся в эксплуатации на железных дорогах Российской Федерации по состоянию технической документации на 01.01.2001 г.

1.2. Требования настоящей Инструкции обязательны для предприятий и организаций путевого хозяйства федерального железнодорожного транспорта.

1.3. Транспортирование машин должно производиться в соответствии с разделами I, III, и IV настоящей Инструкции, а также нормативными актами МПС России об условиях обращения конкретных машин и инструкциями (руководствами) по эксплуатации соответствующих машин.

Условия транспортирования машин определены разделом II настоящей Инструкции.

1.4. Каждая транспортируемая машина должна иметь отличительные знаки и надписи, предусмотренные Правилами технической эксплуатации железных дорог Российской Федерации (ПТЭ).

1.5. Транспортирование машин должно производиться с соблюдением требований следующих нормативных актов:

а) правила технической эксплуатации железных дорог Российской Федерации;

б) инструкция по сигнализации на железных дорогах Российской Федерации;

в) инструкция по движению поездов и маневровой работе на железных дорогах Российской Федерации;

г) инструкция по эксплуатации тормозов подвижного состава железных дорог;

д) инструкция по обеспечению безопасности движения поездов при производстве путевых работ;

е) правила по охране труда при содержании и ремонте железнодорожного пути и сооружений;

ж) технические условия погрузки и крепления грузов;

з) правила перевозок автотракторной техники на железнодорожном транспорте;

и) правила пожарной безопасности на железнодорожном транспорте;

к) инструкция по эксплуатации или инструкция по транспортированию на соответствующую машину;

л) иные нормативные акты МПС России и железных дорог.

1.6. Транспортирование машин может производиться только после

приведения их в транспортное положение в соответствии с настоящей Инструкцией.

1.7. Порядок постановки машин в составе грузового поезда и скорость их транспортирования определяются Нормами допускаемых скоростей движения специального подвижного состава (мотовозов, дрезин, специальных автомотрис, железнодорожно-строительных машин) по железнодорожным путям колеи 1520 (1524) мм федерального железнодорожного транспорта или указаниями МПС России по условиям обращения соответствующих машин. При отсутствии указаний МПС России порядок постановки машин в составе грузового поезда и скорость транспортирования определяется инструкциями по эксплуатации на машины, утвержденными МПС России.

1.8. Каждая транспортируемая машина сопровождается проводниками. Допускается транспортирование без проводников порожних хоппер-дозаторов.

Порядок сопровождения машин при их транспортировании и обязанности проводников определены разделами V и VI настоящей Инструкции.

1.9. Транспортируемая машина снабжается средствами сигнализации и необходимым инвентарем в соответствии с разделом VII настоящей Инструкции.

1.10. Машины, не упомянутые в настоящей Инструкции, приводятся в транспортное положение в соответствии с эксплуатационной документацией, комплектуемой заводом-изготовителем.

II. Условия транспортирования машин

2.1. Транспортирование машин может производиться:

а) по открытому для движения поездов перегону;

б) по закрытому для движения поездов перегону, т.е. при следовании со станции, ограничивающей свободный перегон, к месту путевых работ и обратно.

2.2. При следовании машин по открытому для движения поездов перегону для различных машин, в зависимости от их устройства и конструктивных особенностей, разрешаются следующие виды транспортирования:

а) в составе грузового поезда;

б) с отдельным локомотивом;

в) в составе хозяйственного поезда;

г) транспортирование своим ходом;

д) транспортирование в погруженном состоянии на железнодорожных платформах.

2.3. Порядок приведения машин в транспортное положение при их транспортировании своим ходом, отдельным локомотивом, а также в составе грузового или хозяйственного поезда определен в разделе III настоящей Инструкции, а при транспортировании на платформах - в разделе VI настоящей Инструкции.

2.4. При транспортировании машин в составе грузового поезда роспуск с сортировочных горок запрещается.

III. Порядок приведения машин в транспортное положение

3.1. Общие требования

3.1.1. При всех видах транспортирования машин по открытому или закрытому для движения поездов перегону необходимо:

а) привести все рабочие органы машины, навесное оборудование, агрегаты и механизмы в габарит подвижного состава по ГОСТ 9238-83, в соответствии с требованиями конструкторской документации на конкретную машину.

б) закрепить стопорными устройствами все механизмы, узлы и детали, исключив возможность их смещения, движения и случайного падения на путь или самопроизвольного включения;

в) закрепить все находящиеся на платформах или в кабинах и кузовах машин, а также на прицепленных к ним железнодорожных вагонах и платформах снятые с машин узлы и детали, оборудование и инвентарь;

г) слить воду из систем охлаждения двигателей и топливо из топливных баков; перекрыть краны топливопроводов, систем охлаждения и смазки (за исключением случая транспортирования машин своим ходом или в составе хозяйственного поезда);

д) установить в нулевое положение все рукоятки управления контроллеров, автоматов, выключателей, разомкнуть рубильники, а распределительные щиты и шкафы закрыть на замки (за исключением случая транспортирования машин своим ходом или в составе хозяйственного поезда);

е) аккумуляторные батареи должны быть заряжены и отключены от цепи; провода аккумуляторных батарей отсоединяются от клемм аккумуляторов (за исключением случая транспортирования машин своим ходом или в составе хозяйственного поезда).

ж) при транспортировании машин своим ходом, они должны быть оборудованы исправной поездной радиостанцией и системой безопасности движения типа КЛУБ - П для ССПС - 2-ой категории и КЛУБ - УП для ССПС - 1-ой категории, с отметкой об их исправности в журнале технического состояния машины формы ТУ - 152.

3.1.2. Все транспортные крепления машин: стопорные механизмы, штыревые крепления, винтовые стяжки, скобы, защелки, цепи и другие элементы транспортных креплений должны быть исправны и надежны. При приведении машин в транспортное положение все детали транспортных креплений подвергаются осмотру и проверке. Трещины, помятость, срывы ниток или искажение профиля резьбы, погнутые болты, проушины, валики и другие дефекты на деталях транспортных креплений не допускаются.

3.1.3. В случаях длительного транспортирования машины (более 5 суток) все металлические неокрашенные поверхности элементов машины покрываются тонким слоем антикоррозионной смазки (смазка УС ГОСТ 1033-79) в соответствии с порядком консервации машины.

Установленные на машинах двигатели, компрессоры и другие агрегаты консервируются согласно инструкциям заводов-изготовителей. Канаты грузоподъемных устройств и лебедок смазываются канатной смазкой 39у (ТУ 38.УССР 2-01-335-80).

3.1.4. В транспортном положении окна кузовов, кабин машин плотно закрываются, а двери запираются на ключ (за исключением случаев транспортирования машин своим ходом). Ключи от дверей транспортируемых машин хранятся у сопровождающих машину проводников. Транспортирование машин с выбитыми стеклами окон или дверей не допускается.

3.1.5. Ходовые части, ударно-тяговые устройства и тормозное оборудование машин до их транспортирования подвергаются осмотру и проверке на соответствие нормативным документам МПС России комиссией в составе представителей вагонного хозяйства и отправителя.

У машин, оборудованных автосцепкой, имеющей запоры расцепных рычагов и запорные болты в головках автосцепки, проверить указанные запорные устройства.

3.1.6. Приписанные к машинам инструменты, приспособления, запасные части и съемные узлы при транспортировании упаковываются в ящики и закрепляются в кабине машины, либо перевозятся в вагоне, на платформе, контейнере, следующих вместе с машиной. Техническая документация машины упаковывается в ящик и хранится у старшего проводника, сопровождающего машину или пересылается почтой.

3.1.7. При транспортировании машин на своих осях в составе поезда или с отдельным локомотивом имеющиеся на машинах ручные тормоза отпускаются. Краны машиниста отключаются при помощи кранов двойной тяги и комбинированных кранов. Разобщительные краны тормозной воздушной магистрали приводятся в положение для следования в составе поезда согласно инструкции по эксплуатации данной машины.

Воздухораспределитель машины устанавливается на равнинный и средний режим или режим короткосоставного поезда.

В случае необходимости транспортирования машины на ремонтное предприятие способ ее доставки определяется грузоотправителем машины с учетом фактического ее состояния.

3.1.8. Порядок приведения в транспортное положение каждого типа машины указан в пунктах 3.2 - 3.87 настоящей Инструкции.

3.1.9. При модернизации машин с внесением изменений в конструкцию узлов транспортных креплений рабочих органов, приведение в транспортное положение модернизированных машин производится в соответствии с технической документацией, утвержденной в установленном порядке.

Для дальнейшего изучения скачайте инструкцию, нажав ссылку "Скачать с сервера"

■ Девятиступенчатый суперскаляр, полностью конвейеризованная микроархитектура. Эта функция обеспечивает большее количество магистралей для передачи команд в операционные блоки центрального процессора и включает в себя три оперативных модуля с плавающей запятой, три модуля целых чисел и три модуля адресного вычисления.

■ Суперскалярная архитектура, полностью конвейеризованный модуль вычисления с плавающей запятой. Эта функция обеспечивает более быстрое выполнение операций и компенсирует существовавшее ранее отставание процессоров AMD от процессоров Intel.

■ Аппаратная поддержка упреждающей выборки данных. Эта функция извлекает необходимые данные из системной памяти и для уменьшения времени доступа помещает их в процессор, в частности в кэш-память первого уровня.

■ Улучшенные буфера быстрого преобразования адреса (TLB). Позволяют процессору значительно ускорить доступ к хранящимся данным, избегая при этом дублирования данных или останова из-за отсутствия оперативной информации.

Описанные конструктивные улучшения позволяют увеличить объем вычислений, выполняемых процессором в течение каждого такта, благодаря чему "медленные" Athlon XP

Если Вы найдете какие либо опечатки, ошибки или подозрительные неточности то обязательно сообщите об этом администрацию сайта (Сделать это можно здесь )

Аналитические компании, такие как Gartner и META Group, и многочисленные поставщики IT-продукции сходятся во мнении, что семейство 64-разрядных процессоров окажет огромное воздействие на развитие IT-рынка в ближайшие годы.

сли рынок 32-разрядных процессоров, таких как Intel Pentium 4 и AMD Athlon XP, является достаточно массовым и хорошо известен потребителям, то популярность 64-разрядных процессоров не столь очевидна. Далеко не все пользователи ПК смогут назвать хотя бы один-два 64-разрядных процессора. И это не случайно, ибо такие процессоры не являются массовыми. Их рынок узкоспециализирован и ориентирован прежде всего на корпоративные сети для работы с приложениями, которым необходимы большой вычислительный ресурс и исключительная надежность систем, — например с приложениями для реального бизнеса, использующими колоссальные объемы оперативной памяти для различных ресурсоемких приложений (больших баз данных, систем интеллектуального бизнес-анализа, систем управления ресурсами предприятия, быстродействующих баз данных, хранящихся в оперативной памяти, и т.д.), широко востребованных в банковской, производственной, инженерной и научно-исследовательской деятельности.

С точки зрения корпоративных заказчиков, 64-разрядная архитектура обладает двумя колоссальными преимуществами перед 32-разрядной. Во-первых, она позволяет работать с огромными объемами данных, что делает ее идеальным выбором для операций с большими базами данных и с требовательными к ресурсам корпоративными приложениями. Во-вторых, она позволяет значительно расширить объем адресуемой памяти компьютера (до 264 байт). Возможность держать в памяти целые базы данных многократно ускоряет работу и СУБД, и так необходимых всем нам защищенных Интернет-приложений.

Несмотря на то что, по мнению большинства аналитиков, в скором времени 64-разрядная архитектура станет массовой, сегодня 64-разрядные процессоры используются исключительно в high-end-серверах масштаба предприятия. Здесь, правда, нужно сделать одну оговорку. К примеру, на сайте корпорации Intel 64-разрядный процессор Intel Itanium 2 позиционируется и как процессор для серверов, и как процессор для высокопроизводительных рабочих станций. По всей видимости, отнесение Intel Itanium 2 к процессорам для рабочих станций — это своего рода попытка подготовить аудиторию к постепенному переходу на 64-разрядные архитектуры. Во всяком случае, реальных примеров того, что какая-либо компания представила рабочую станцию на процессорах Intel Itanium 2, пока нет, и они вряд ли появятся в ближайшем будущем.

Причин тому несколько, и одна из главных — стоимость процессоров и решений на их основе. Так, сервер, построенный на 64-разрядной платформе, стоит не один десяток и даже, возможно, сотни тысяч долларов, и его, естественно, под силу приобрести только крупным корпоративным заказчикам.

Другой причиной является отсутствие пользовательской 64-разрядной операционной системы, которая могла бы претендовать на роль массовой, такой, например, как Windows XP, а также отсутствие соответствующих 64-разрядных приложений.

Понятно, что когда говорят о серверных системах, то прежде всего имеют в виду многопроцессорные системы. Поэтому одним из кардинальных отличий всех 64-разрядных процессоров является возможность построения на их основе многопроцессорных масштабируемых систем. Именно многопроцессорные конфигурации позволяют добиться непревзойденного уровня вычислительной мощности за счет параллельного выполнения на всех процессорах нескольких задач или нескольких потоков одной задачи одновременно.

Однако прежде чем переходить к рассмотрению конкретных примеров 64-разрядных процессоров, ознакомимся с основами процессорной архитектуры.

Традиционно по системе команд и архитектуре различают CISC- и RISC-процессоры.

RISC (Reduced Instruction Set Computer) — это процессоры с сокращенной системой команд, отличающиеся однородным набором регистров. Аппаратная реализация такой архитектуры позволяет с небольшими затратами выполнять эти инструкции за минимальное число тактов.

CISC (Complete Instruction Set Computer) — это процессоры с полным набором инструкций. Состав и назначение их регистров крайне неоднородны, широкий набор усложняет декодирование инструкций, на что расходуются аппаратные ресурсы. Возрастает и число тактов, необходимое для выполнения инструкций.

Деление процессоров на CISC и RISC становится все более условным. К примеру, современные процессоры для ПК (Intel Pentium, AMD Athlon) с архитектурой x86 представляют собой своеобразный симбиоз CISC- и RISC-архитектур. Так, относительно потока команд в формате x86 — это классические CISC-процессоры. Однако в самих процессорах команды формата x86 претерпевают декодирование на микрооперации, подобные RISC-командам, и в этом смысле ядро таких процессоров имеет RISC-архитектуру.

Если обратиться к истории эволюции процессоров, то кроме стремительного роста тактовой частоты можно выделить три тенденции, позволяющие добиться увеличения вычислительной мощности: параллелизм инструкций (ILP), параллелизм потоков (TLP) и размещение нескольких ядер процессора на одном кристалле (CMP). Суть всех технологий сводится к тому, чтобы увеличить количество инструкций, выполняемых процессором за такт (Instruction Per Clock, IPC), что в конечном счете сказывается на такой важной характеристике процессора, как количество операций, выполняемых в единицу времени (Mega Instruction Per Second, MIPS).

Сущность технологии параллелизма на уровне инструкций (Instruction Level Parallelism, ILP) заключается в том, что в процессоре существует несколько параллельно работающих исполнительных блоков. В этом случае возможно параллельное выполнение нескольких процессорных инструкций одновременно. Такая многозадачность в том или ином виде реализована во всех современных процессорах. Однако наращивание исполнительных блоков имеет свои жесткие ограничения. Связано это с тем, что при увеличении их числа необходимо увеличивать и количество регистров процессора для обеспечения необходимой загрузки блоков. В среднем число регистров должно возрастать квадратично числу исполнительных блоков.

Как уже отмечалось, в CISC-процессорах набор регистров сложный и неоднородный, поэтому увеличение числа исполнительных блоков в процессорах с архитектурой x86 связано с определенными трудностями.

RISC-архитектуры с простым набором регистров в этом смысле более благополучны и позволяют достигнуть большего значения ILP.

Другая проблема, возникающая при увеличении числа исполнительных блоков, — это требования, налагаемые на кэш первого уровня (L1). Для того чтобы обеспечить загрузку большого числа исполнительных блоков, кэш L1 должен иметь достаточно большие емкость и пропускную способность.

Другим способом увеличения производительности процессоров является реализация параллелизма на уровне потоков (Thread Level Parallelism, TLP), то есть параллельного исполнения процессором нескольких потоков инструкций. В отличие от технологии ILP, которая не противостоит TLP, а дополняет ее, распараллеливание в данном случае происходит не на аппаратном, а на программном уровне, то есть прибавку в скорости от TLP получают многопоточные программы, оптимизированные для исполнения на многопроцессорных системах.

Указанная технология должна обеспечить более эффективную загрузку исполнительных блоков, при этом потоки разделяют одни и те же функциональные устройства процессора. Классическим примером успешной реализации параллелизма на уровне потоков является технология Hyper-Threading, использованная в процессорах Intel Pentium и Intel Xeon.

Однако более радикальным средством повышения производительности процессора является интегрирование нескольких процессорных ядер на одном кристалле (Chip MultiProcessing, CMP). В данном случае получается практически многопроцессорная конфигурация, но расположение ядер на одном кристалле обеспечивает гораздо более высокую скорость обмена между процессорами, чем при использовании любых внешних шин. В настоящее время технология CMP реализована в процессорах IBM Power 4, а в недалеком будущем она будет использована и в процессорах семейства Itanium и SPARC.

Итак, после краткого рассмотрения основных способов увеличения вычислительной мощности современных процессоров давайте поближе познакомимся с 64-разрядными процессорами, используемыми в high-end-серверах.

Конечно, рассмотреть в пределах одной статьи все 64-разрядные процессоры не представляется возможным, тем более что перспективы некоторых из них весьма туманны, а иные уже вообще канули в вечность. Поэтому в нашем обзоре мы остановимся на наиболее популярных представителях 64-разрядных процессоров: семействе Intel Itanium, SPARC, IBM Power и AMD Opteron.

Процессоры семейства Intel Itaniumроцессоры семейства Intel Itanium отличаются от всех остальных 64-разрядных процессоров абсолютно новой архитектурой. В этом смысле они не относятся ни CISC-, ни к RISC-процессорам, а представляют собой реализацию новой концептуальной архитектуры EPIC (Explicitly Parallel Instruction Computing). Однако архитектуру процессоров семейства Intel Itanium принято называть IA-64, а не EPIC. Дело в том, что EPIC — это общая концепция, которая может реализовываться различными способами. Например, так же, как RISC-архитектура, архитектура EPIC может иметь различные наборы команд. Поэтому когда говорят об архитектуре IA-64, реализующей идеологию EPIC, то подразумевают вполне конкретный набор команд. Следовательно, IA-64 — это практическая (и в настоящее время единственная) реализация концепции EPIC.

Базовые принципы EPIC — архитектуры с явно выраженным параллелизмом на уровне инструкций — были заложены еще в начале 90-х в Иллинойсском университете, причем сама по себе архитектура EPIC явилась логическим продолжением концепции VLIW (Very Long Instruction Word), разработанной Тьюрингом еще в 1946 году.

Подробное описание архитектуры EPIC даже в концептуальном плане достаточно сложно, поэтому мы лишь поверхностно рассмотрим ее базовые идеи.

В традиционных RISC- и CISC-процессорах распараллеливание на уровне инструкций для их одновременного выполнения на нескольких исполнительных блоках происходит на аппаратном уровне. Однако для того, чтобы несколько инструкции можно было выполнять одновременно, они должны быть независимы друг от друга. Если, к примеру, имеются две следующие друг за другом инструкции: С=A+B, D=C+G, то понятно, что вычислять значение D нельзя до тех пор, пока не вычислено значение С; то есть эти инструкции являются зависимыми и не предполагают одновременного выполнения. Принципиальное отличие архитектуры EPIC от архитектуры суперскалярных процессоров как раз и заключается в том, каким образом определяются для распараллеливания независимые инструкции. В суперскалярных процессорах этот вопрос решается на аппаратном уровне, для чего используется сложное аппаратное решение, позволяющее производить переупорядочивание инструкций (Out-Of-Order), — это и буферы переупорядочивания, и блоки предсказания ветвлений, и т.д. Понятно, что с увеличением числа исполнительных блоков должны возрастать и сложность алгоритма предсказания, и размеры соответствующих блоков, поэтому аппаратное решение распараллеливания программы на уровне инструкций имеет ограничения.

В EPIC-архитектуре независимые команды выделяются не на аппаратном уровне, а на уровне компилятора. Компилятор сначала обнаруживает все зависимости между данными, а затем определяет, как их развязать, что достигается за счет переупорядочивания следования инструкций. Из независимых инструкций формируются группы (длинные инструкции), которые затем возможно выполнять одновременно на нескольких исполнительных блоках процессора. Таким образом, в EPIC-архитектуре параллелизм достигается на программном уровне. Конечно, когда формирование независимых инструкций происходит на уровне компилятора, достигается значительно более высокий уровень параллелизма, чем при аппаратном решении (как в суперскалярных процессорах). Причина состоит в том, что для обеспечения наиболее полного распараллеливания необходимо «просматривать» достаточно длинные фрагменты кода, то есть осуществлять трассировку программы. В случае же аппаратной реализации осуществить такую трассировку на множество инструкций довольно сложно. Кроме того, подобному отслеживанию препятствуют и ветвления в программе, для «борьбы» с которыми используется спекулятивное прогнозирование дальнейшего хода программы, которое реализуется в RISC-процессорах аппаратно, а в EPIC-процессорах посредством компилятора.

Итак, главная особенность EPIC-архитектуры по сравнению с RISC-архитектурой заключается в том, что удается добиться более высокого уровня распараллеливания на уровне команд и, как следствие, достигнуть более высокого значения IPC.

Несмотря на очевидные преимущества EPIC-архитектуры, она имеет и свои недостатки (к сожалению, идеальной процессорной архитектуры нет — во всем нужно искать золотую середину). Самый главный ее недостаток заключается в том, что компилятор должен быть очень жестко привязан к конкретной архитектуре процессора. Действительно, если компилятор не будет знать о количестве исполнительных блоков, то осуществить эффективное распараллеливание будет невозможно. Соответственно при выпуске новой версии процессора с большим количеством исполнительных блоков придется и менять компилятор, и перекомпилировать все ПО для корректной работы на новом процессоре. Для того чтобы частично решить данную проблему, в процессорах семейства Itanium с архитектурой IA-64 используются фиксированное количество независимых инструкций в группе (по три в группе), что, с одной стороны, конечно, не очень удобно в отношении конкретного процессора, но, с другой стороны, позволяет в будущем менять количество исполнительных блоков.

После краткого рассказа об EPIC-архитектуре перейдем к рассмотрению семейства процессоров Intel Itanium.

История процессора Intel Itanium начинается с 1994 года, когда компании Intel и HP, основываясь на опыте НР в области высокопроизводительных компьютерных систем и на возможностях Intel по разработке и производству широко доступных процессоров, объединили свои усилия, образовав альянс по разработке новой высокопроизводительной 64-разрядной архитектуры. В результате в 1997 году был разработан новый набор команд ISA (Instruction Set Architecture), а в октябре того же года на конференции Microprocessor Forum (г.Сан-Хосе, шт.Калифорния) впервые была публично продемонстрирована архитектура первого 64-разрядного процессора Intel под кодовым названием Merced.

В июле 2002 года было объявлено о создании нового 64-разрядного процессора Intel Itanium 2, названного McKinley, и 30 июня нынешнего года компания Intel представила новую версию процессора Intel Itanium 2, известного ранее под кодовым названием Madison.

Мало того — уже запланирован выпуск следующих моделей процессоров: Deerfield и Montecito. Процессор Deerfield будет создан на основе 0,13-микронной технологии, тогда как процессор Montecito — уже на основе 90-нанометровой технологии.

В отличие от предыдущей версии процессора Intel Itanium 2 (McKinley), изготовлявшейся по 0,18-микронному технологическому процессу, Intel Itanium 2 (Madison) производится по 0,13-микронной технологии. В результате перехода на новую технологию удалось снизить напряжение питания ядра процессора (1,3 вместо 1,5 В), значительно увеличить размер кэш-памяти третьего уровня и поднять тактовую частоту процессора. Так, новый процессор имеет кэш-память третьего уровня (L3) объемом до 6 Мбайт, кэш-память второго уровня (L2) объемом 256 Кбайт и кэш-память первого уровня (L1) объемом 32 Кбайт. Тактовая частота процессора составляет 1,5 ГГц — вместо 1,0 ГГц в предыдущей версии процессора.

В процессоре Intel Itanium 2 имеется шесть исполнительных конвейеров длиной по восемь стадий, состоящих из 11 каналов. Учитывая, что в каждую группу входит по три независимые инструкции, процессор может одновременно выполнять две группы инструкций и, следовательно, выполнять шесть инструкций за один системный такт.

Кроме того, в процессоре имеется 328 встроенных регистров, из которых 128 — это 64-разрядные целочисленные регистров, 128 — это 82-разрядные регистры для данных с плавающей запятой, 64 — это однобитные регистры для предсказания ветвлений и 8 — это регистры с адресами переходов. Регистры выделяются динамически, а если их не хватает, то часть регистров записывается в системную память и становится доступной для команд.

Процессор Intel Itanium 2 использует 400-мегагерцевую, 128-разрядную системную шину, пропускная способность которой соответственно равна 400 МГцЅ128 бит = = 6,4 Гбайт/с.

В процессоре Intel Itanium 2 реализован ряд ключевых функций повышения надежности и готовности, разработанных для процессора Intel Itanium. Новаторская архитектура Machine Check Architecture (MCA) и широкое применение технологии обнаружения и исправления ошибок (ECC) позволяют обнаруживать ошибки на уровне единичных разрядов и предотвращать потери данных. В сочетании с возможностями уровня системы, такими как горячая замена компонентов, новый процессор позволяет создавать серверы и рабочие станции с безупречной надежностью и готовностью.

В целом использование процессоров Intel Itanium 2 позволяет создавать системы с количеством до 32 процессоров в симметричной многопроцессорной (SMP) конфигурации и вплоть до 512 процессоров при построении кластерных систем.

Процессоры семейства SPARCSPARC (Scalable Processor ARChitecture) — это масштабируемая процессорная архитектура, являющаяся открытым стандартом процессорной архитектуры. Права на эту архитектуру принадлежат некоммерческой ассоциации SPARC International (www.sparc.org). Лицензиаты архитектуры SPARC должны следовать стандарту IEEE на систему команд SPARC, но обладают свободой выбора остальных параметров процессора.

Архитектура SPARC основана на спецификации RISC (Reduced Instruction Set Computer), созданной Дэйвом Паттерсоном (Dave Patterson) в Университете Беркли. В 1984 году команда инженеров компании Sun Microsystems начала работы по определению архитектуры SPARC, а в 1986 году появился первый 32-битный процессор SPARC 86900 «Sunrise», изготовленный на микросхеме. Этот первый процессор работал на частоте 16,67 МГц и имел производительность 10 MIPS. В марте 1988 года Fujitsu увеличила тактовую частоту до 25 МГц, создав процессор с производительностью 15 MIPS.

В 1989 году для развития и продвижения этой перспективной открытой архитектуры была создана независимая ассоциация SPARC International, которой были переданы права на архитектуру SPARC. В настоящее время ассоциация насчитывает более 50 членов.

В 1986 году SPARC International опубликовала 7-ю версию архитектуры SPARC. Версия 8 появилась в 1990 году, а в начале 90-х существовало уже более 20 реализаций SPARC-процессоров от таких производителей, как Fujitsu (SPARCIite), Ross Technology (HyperSPARC) и Sun Microsystems (SuperSPARC и microSPARC).

В 1993 году была представлена 64-битная версия спецификации SPARC v.9. Первым 64-битным процессором SPARC в декабре 1995 года стал процессор SPARC64 I от Fujitsu.

В настоящее время компания Fujitsu использует процессоры четвертого (SPARC64 IV) и пятого (SPARC64 V) поколений. Эти суперскалярные 64-разрядные RISC-процессоры основаны на архитектуре SPARC v.9, что обеспечивает 100-процентную совместимость с приложениями, написанными под OC Solaris для SPARC-платформ разных производителей.

Максимальная частота процессора SPARC64 IV составляет 788, 800 и 810 МГц, а первые версии процессоров SPARC64 V (рис. 1 ) работают с частотой 1,3 и 1,35 ГГц. Ожидается, что в нынешнем году тактовая частота процессора увеличится до 1,8 ГГц, а в следующем — до 2,5 ГГц, что станет возможным благодаря переходу на новые технологические процессы с проектной нормой 0,1 мкм. В дальнейших планах компании Fujitsu — выпуск в 2005 году процессоров с тактовой частотой 3 ГГц (по два физических процессора на одном кристалле), а в 2007-м — выпуск процессоров с тактовой частотой 6 ГГц (по четыре процессора на одном кристалле).

Увеличение производительности процессора SPARC64 V достигается за счет выполнения большего числа операций за один такт, а также за счет увеличения числа тактов в секунду. SPARC64 V выполнен по передовой медной 0,13-микронной технологии и содержит 191 млн. транзисторов. Кэш-память первого уровня (L1) делится на память команд (128 Кбайт) и данных (128 Кбайт), а кэш-память второго уровня (L2) составляет 2 Мбайт и имеет четыре канала доступа. При этом сама память L2 является неблокируемой, то есть исключающей конфликт при доступе к строкам кэша, когда код и данные используют одну кэш-память.

Скорость упреждающей выборки из кэш-памяти — более 40 Гбайт/с, а скорость записи в кэш-память — свыше 20 Гбайт/с.

В процессоре SPARC64 V реализуется одновременное декодирование и выдача четырех инструкций за такт, используются современный механизм предсказаний переходов, прогнозирование выборки и параллельное, неупорядоченное выполнение команд (out-of-order processing) на шести арифметических модулях. Одновременно могут выполняться до шести стандартных операций или до четырех операций с плавающей точкой.

В конструкции SPARC64 V основной акцент сделан не на тактовой частоте, а на числе выполняемых инструкций за такт. Это обеспечивает сравнительно небольшое энергопотребление (57 Вт), а значит, и тепловыделение. Следовательно, процессоры не требуют дорогостоящих систем охлаждения и меньше подвержены сбоям.

Другой характерной особенностью процессора SPARC64 V является набор средств обеспечения высокой готовности и надежности. К таким средствам относятся:

• автоматический повтор инструкций;

• встроенные в кристалл функции контроля четности;

• защита кодом коррекции ошибок ECC;

• устройства проверки ошибок;

• возможность частичного отключения кэш-памяти;

• программное отключение процессора.

Автоматический повтор инструкций заключается в том, что в случае эпизодических «мягких» ошибок, не связанных с аппаратной неисправностью, процессор автоматически перезапускает на аппаратном уровне обработку инструкции, на которой произошла ошибка. Если в результате повторных запусков инструкций ошибка не исправляется, процессор сообщает об ошибке операционной системе и возлагает обработку этой ошибки на ОС. Данный метод на 98% сокращает обращения к OC из-за «мягких» ошибок.

В процессоре SPARC64 V поддерживается контроль четности как в вычислительном блоке, так и в регистрах. С учетом возможности повтора инструкций это значительно сокращает ошибки данных и инструкций.

Защита кодом коррекции ошибок ECC применяется для исправления однобитных и обнаружения двухбитных ошибок во встроенной кэш-памяти L2 как для данных, так и для тэгов. ECC также применяется к данным в кэш-памяти L1, а тэги 1-го уровня дублируются в кэш-памяти L2. При копировании из кэш-памяти L1 в кэш-память L2 ошибки разрядов в памяти тэгов автоматически корректируются.

Кроме того, механизм ECC применяется на внутренних процессорных высокоскоростных шинах с малым временем задержки (скорость чтения 40 Гбайт/с).

В SPARC64 V добавлены устройства проверки ошибок. Эти устройства контролируют регистры процессора, внутренние пути данных, арифметико-логические устройства (ALU), массивы данных и тэгов кэша, буфер быстрого преобразования адреса (Translation Look aside Buffer, TLB), который проверяется еще и на четность.

При возникновении постоянной ошибки процессор может аппаратно, без участия ПО, произвести частичное отключение кэш-памяти, то есть вывести из работы определенные участки памяти или каналы доступа к кэш-памяти.

Если же число корректируемых ошибок в процессоре превышает пороговое значение, ОС интерпретирует это состояние как невосстановимую ошибку и может логически отключить такой процессор.

Процессор AMD Opteronреди всех 64-разрядных процессоров AMD Opteron является самым молодым. Выполнен данный процессор по 0,13-микронному технологическому процессу и имеет размер кристалла 200 мм2.

Это семейство процессоров появилось совсем недавно и, в отличие от всех остальных 64-разрядных процессоров, имеет ряд особенностей, позволяющих позиционировать данный процессор для построения не только мощных серверов, но и высокопроизводительных многопроцессорных рабочих станций.

Итак, если говорить коротко, то основу процессора составляет процессорное ядро Hammer с поддержкой архитектуры x86-64 ISA, интегрированный контроллер памяти и интегрированный интерфейс Hyper Transport.

Кэш первого уровня (L1) процессора AMD Opteron остался точно таким же, как и в процессорах семейства Athlon XP, то есть он имеет общий размер 128 Кбайт и разделен на кэш данных (D-cache) и кэш инструкций (I-cache), каждый размером по 64 Кбайт. К тому же кэш L1 остался ассоциативным двухканальным с размером кэш-блока 64 байт. Кэш инструкций поддерживает два набора дескрипторов (тэгов): fetch port (порт выборки) и snoop (слежения).

Кэш данных поддерживает 30-битный физический и 48-битный линейный адрес. Таким образом кэш поддерживает уже три типа тэгов: port A, port B и snoop. Кроме того, кэш данных поддерживает две 64-битные операции записи/чтения за один такт в различные банки кэша.

Кэш второго уровня (L2) может иметь максимальный размер до 1 Мбайт, и является эксклюзивным по отношению к кэшу L1, 16-канальным ассоциативным.

Кроме того, кэш L2 содержит указатели предсказания ветвлений (branch prediction bits) и предварительно декодированные инструкции. Еще одним нововведением является увеличенная вдвое (по сравнению с процессором Athlon XP) скорость передачи между кэшами L2 и L1.

Как и в большинстве современных х86-совместимых процессоров, имеющих внутреннюю RISC-архитектуру, в процессоре Opteron внешние CISC-команды декодируются во внутренние RISC-инструкции, для чего используется декодер команд.

В процессоре AMD Opteron реализуется одновременное декодирование и выдача шести инструкций за такт (используются два декодера). После прохождения декодера инструкции (по три за каждый такт) поступают во временный буфер хранения, главная задача которого заключается в диспетчеризации трех инструкций за такт по функциональным устройствам, то есть временный буфер хранения распределяет инструкции в зависимости от их назначения и посылает их в целочисленный планировщик для работы с целыми числами, а инструкции для работы с вещественными числами — в планировщик для работы с вещественными числами.

Планировщик для работы с вещественными числами (FPU) рассчитан на 36 инструкций (как и в процессоре Athlon XP), и его основная задача заключается в том, чтобы распределять команды по исполнительным блокам по мере их готовности. Таким образом, просматривая все 36 поступающих инструкций, планировщик переупорядочивает следование команд, строя спекулятивные предположения о дальнейшем ходе программы так, чтобы создать несколько полностью независимых друг от друга очередей инструкций, которые можно выполнять параллельно. В процессоре Opteron имеются три исполнительных блока для работы с вещественными числами, поэтому FPU-планировщик должен формировать по три инструкции за такт, направляя их на исполнительные блоки.

Все целочисленные инструкции направляются в планировщик инструкций для работы с целыми числами, рассчитанный на 24 инструкции. Этот планировщик выполняет те же функции, что и FPU-планировщик. Различие заключается в том, что в процессоре Opteron имеется семь функциональных исполнительных блоков для работы с целыми числами.

Как уже отмечалось, одним из главных нововведений процессора Opteron является реализация 64-разрядной архитектуры x86-64 ISA, то есть процессор Opteron является х86-совместимым процессором. В отличие от 64-битной архитектуры IA-64, примененной в процессорах Intel Itanium, x86-64 базируется на существующей архитектуре x86-32.

64-битная адресация, используемая в процессорах Opteron, является полностью совместимой с архитектурой x86-32, поэтому на данном процессоре можно использовать и 32-разрядные приложения — в этом случае возможности процессора задействуются не в полной мере, но тем не менее дополнительная адресация не повредит. Возможность использования обычных 32-разрядных приложений в данном случае особенно значима: для этих процессоров не потребуется специализированных операционных систем и приложений, и нет нужды ждать, пока производители ПО перекомпилируют свои приложения.

Для реализации 64-разрядности в процессоре дополнительно имеется несколько новых регистров, а существующие регистры соответственно расширены с 32 до 64 бит. Так, к восьми регистрам общего назначения добавлено еще восемь 64-битных регистров, использование которых возможно только при соответствующей перекомпиляции программного кода.

Расширение 32-битных регистров до 64-битных осуществляется в точности так же, как в свое время (в период появления процессора i386) 16-битные регистры были расширены до 32-битных.

Для реализации возможности работы как с 32-битными, так и с 64-битными приложениями процессор поддерживает два режима работы: Long Mode и Legacy Mode. В Long Mode используется 64-битный режим работы, причем здесь тоже предусмотрено два режима: 64-битный и Compability Mode (совместимый). 64-битный режим работы — это, собственно, и есть истинный 64-битный режим, задействующий дополнительные регистры процессора и 64-битные расширенные регистры. Для работы в этом режиме требуется соответствующая перекомпиляция ПО.

В режиме Compability Mode дополнительные регистры не задействуются, а в регистрах общего назначения используется только 32-битная часть. Единственное, что в данном случае напоминает о 64-битной архитектуре — это использование 64-разрядной адресации и 64-битной операционной системы. В этом режиме не требуется перекомпиляции приложений для их нормальной работы.

В режиме Legacy Mode используется 32-разрядная операционная система, то есть 32-разрядная адресация. Кроме того, не задействуются дополнительные регистры, а в регистрах общего назначения используются только первые 32 бита. Следовательно, Legacy Mode — это обычный 32-битный режим работы процессора.

Одной из главных конструктивных особенностей процессора Opteron является интегрированный в сам процессор контроллер памяти, который традиционно располагается в северном мосте чипсета на системной плате.

Контроллер памяти процессора поддерживает DDR-память и имеет ширину шины 64 или 128 бит. В последнем случае речь идет о двухканальной памяти, которая реализуется в серверных процессорах.

Новейшим революционным нововведением процессора является поддержка шины Hyper Transport. В основу этой шины положены две концепции: универсальность и масштабируемость.

Универсальность шины Hyper Transport заключается в том, что это шина позволяет связывать между собой не только процессоры, но и другие компоненты системной платы.

Масштабируемость данной шины заключается в том, что она позволяет наращивать пропускную способность по мере необходимости.

Устройства, связываемые по шине Hyper Transport, соединяются согласно принципу «точка-точка» (peer-to-peer), что подразумевает возможность связывания в цепочку множества устройств без использования специализированных коммутаторов.

Для обеспечения масштабируемости шина Hyper Transport может иметь магистраль шириной 2, 4, 8, 16, и 32 бит в каждом направлении. Кроме того, предусматривается возможность работы на различных тактовых частотах (от 200 до 800 МГц). Таким образом, пропускная способность шины Hyper Transport меняется от 200 Мбит/с при использовании частоты 200 МГц и двух двухбитных каналов до 12,8 Гбит/с при использовании тактовой частоты 800 МГц и двух 32-битных каналов.

Так, в настоящей версии процессора AMD Opteron реализованы три 16-битных интерфейса шины Hyper Transport, каждая из которых обладает пропускной способностью 3,2 Гбайт/с в одном направлении. Это позволяет создавать 2-, 4- и 8-процессорные серверы на базе AMD Opteron.

Процессор IBM Power4роцессор IBM Power4 (рис. 2 ) — это классический пример реализации технологии CMP (Chip MultiProcessing). В одном процессоре интегрированы два процессорных ядра, в каждом из которых имеется собственный кэш первого уровня (L1) данных и инструкций. Кэш инструкций имеет емкость 64 Кбайт, а кэш данных — 32 Кбайт (см. таблицу ).

Кэш второго уровня (L2) является общим (разделяемым), причем доступ к кэшу L2 осуществляется через коммутатор CIU (Core Interface Unit). Размер кэша L2 составляет 1,41 Мбайт.

Работой кэша L2 управляют три отдельных контроллера, каждый из которых может выдавать по 32 байта за такт.

Коммутатор CIU связан с каждым из процессоров по отдельной шине, которая делится на 256-разрядную шину для выборки инструкций, 256-разрядную шину загрузки данных и 64-разрядную шину для записи результатов.

Для связи коммутатора CIU с каждым из трех контроллеров кэша L2 используются 64-разрядные (для записи результатов в кэш) и 256-разрядные (для загрузки данных из кэша) шины.

Кроме того, каждый из процессоров связан с блоком (NC Unit) для поддержки некэшируемых операций.

Кроме коммутатора CIU, осуществляющего взаимодействие между ядрами процессоров и кэшем L2, на кристалле расположен еще один коммутатор, называемый Fabric Controller. Этот коммутатор осуществляет управление потоками данных между памятью, кэшами L2 и L3, а также между чипами.

Контроллер кэша 3-го уровня (L3) и контроллер памяти размещены на том же кристалле. Сам же кэш L3 размешается на отдельном кристалле и может иметь размер до 32 Мбайт. Для связи коммутатора Fabric Controller с кэшем L3, работающим на 1/3 частоты процессора, и памятью используются две 128-битные шины.

Теперь обратимся к архитектуре ядра процессора IBM Power4. Как уже отмечалось, на одном кристалле интегрированы два абсолютно идентичных ядра процессора, то есть реализуется двухпроцессорная SMP-модель. По своей внутренней архитектуре (рис. 3 ) процессор Power4 является классическим суперскалярным процессором с неупорядоченным спекулятивным (Out-Of-Order) исполнением инструкций. Поэтому те, кто знаком с архитектурой десктопных процессоров AMD и Intel, по своей архитектуре также являющихся суперскалярными, сразу обнаружат, что между Power4 и этими процессорами много общего.

При работе процессора инструкции, загружаемые из кэша L1 (I-cache), подвергаются декодированию, «взлому» и группировке. За каждый такт из L1-кэша возможна выборка восьми инструкций. Под взломом (cracked) понимают разбиение инструкций на более мелкие операции, именуемые IOPs. Если одна инструкция разбивается на две IOps, их называют «взломанными» (cracked). Если же разбиение происходит на большее количество микроинструкций, то их называют милликодированными (millicoded).

Поскольку в процессоре предусмотрено беспорядочное (Out-Of-Order) выполнение инструкций, нарушающее порядок их следования, то для упрощения логики, отвечающей за отслеживание большого числа беспорядочно исполняющихся инструкций, используется формирование групп. Каждая группа состоит максимум из пяти взломанных инструкций IOPs. Для формирования последовательных групп используется понятие слота. Первая инструкция в группе помещается в нулевой слот, вторая — в первый и т.д. Последний (четвертый) слот всегда резервируется для инструкций ветвления.

Взломанные инструкции обязательно должны быть в одной группе. Если для размещения двух взломанных инструкций не хватает места, то процесс заполнения группы прекращается и начинается формирование новой группы. Милликодированные инструкции всегда начинают новую группу.

Группа из пяти инструкций подвергается диспетчеризации. На этом этапе инструкции попадают на порты диспетчеризации, которые выполняют функции шлюзов к функциональным устройствам. Отметим, что за один такт процессора обрабатывается только одна группа из пяти инструкций.

После диспетчеризации группы инструкций контрольная информация о группе сохраняется в таблице групп (Group Completion Table, GCP). Таблица GCP может сохранять записи о 20 группах инструкций. Информация о группе сохраняется в GCP до тех пор, пока группа инструкций не будет полностью выполнена.

В процессоре Power4, как и в любом процессоре со спекулятивным внеочередным выполнением кода, используются эффективные алгоритмы предсказания ветвлений. Для этого применяются модуль сканирования ветвлений (BR Scan) и предсказания ветвлений (BR Predict).

Для достижения высокого уровня параллелизма на уровне инструкций (ILP) в процессоре имеются восемь конвейерных исполнительных блоков с возможностью выполнения до пяти инструкций за такт. Для операций с вещественными числами предусмотрено два исполнительных блока (FP1, FP2), а для операций с целыми числами — также два исполнительных блока (FX1, FX2). Кроме того, имеются два исполнительных блока загрузки/записи (LD1, LD2), устройство для выполнения логических операций (CR) и исполнительный блок переходов (BR). Отметим, что исполнительные блоки для операций с вещественными числами могут выполнять операции сложения и умножения на каждом такте, то есть по четыре операции за такт.

Процессор IBM Power4 сконструирован с учетом возможности построения многопроцессорных SMP-систем. Четыре двухъядерных чипа объединяются в один модуль, насчитывающий уже восемь процессоров. Для связи отдельных чипов друг с другом используются четыре 128-разрядные шины (рис. 4 ), которые подключены к коммутатору Fabric Controller. Эти шины (Chip-Chip Fabric) работают на половинной частоте процессора.

Процессор IBM Power4 допускает возможность организации многопроцессорных систем путем объединения нескольких восьмипроцессорных модулей друг с другом. Всего возможно объединение четырех восьмипроцессорных модулей, следовательно в максимальной конфигурации поддерживается 32-процессорная SMP-система.Для связи отдельных модулей друг с другом используются однонаправленные 64-разрядные шины, которые соединяются по кольцевой топологии (рис. 5 ).

При написании статьи использовались материалы, предоставленные компаниями Intel и Fujitsu Siemens Computers.

Клавиатура — это то устройство, без которого немыслим полноценный компьютер. Во всяком случае, такое положение вещей будет сохраняться до тех пор, пока не придумают какие-нибудь нейроинтерфейсы, в которых текст можно будет вводить одной только силой мысли. Клавиатура — это достаточно простое устройство, однако заядлые геймеры, например, обычно предъявляют к ней целый ряд насущно необходимых требований. В данном обзоре будет рассмотрена известная модель Cougar 700K игровой клавиатуры немецкого производителя Cougar

В этой статье мы рассмотрим HyperX FURY объемом 120 Гбайт — универсальный SSD, позиционируемый компанией Kingston как оптимальное решение для начального уровня для геймеров и энтузиастов. Он имеет толщину всего 7 мм, что позволяет устанавливать его в современные ультрабуки. Второй и не менее интересный SSD в нашем обзоре — это HyperX SAVAGE объемом 480 Гбайт, который был анонсирован весной текущего года и уже появился на прилавках магазинов. Представители линейки HyperX SAVAGE ориентированы на требовательных пользователей, которым необходима высокая производительность дисковой подсистемы ПК для эффективной работы в многозадачном режиме

Российская компания «Бизнес Бюро» объявила о начале продаж планшетного ПК bb-mobile Topol' LTE («Тополь LTE»). Новинка выполнена в прочном металлическом корпусе и оборудована ЖК-дисплеем типа IPS с 8-дюймовым сенсорным экраном, разрешение которого составляет 1280x800 пикселов (16:10)

Если вы часто печатаете фотографии и уже утомились менять картриджи в своем принтере, обратите внимание на МФУ Epson L850. Большой ресурс расходных материалов, великолепное качество отпечатков, широчайший набор функциональных возможностей — вот лишь некоторые из достоинств данной модели

Компания Kingston в очередной раз порадовала пользователей новой бюджетной моделью SSD-накопителя, ориентированной на конечного пользователя и на офисное использование. Кроме того, данный SSD-накопитель серии SSDNow UV300 будет весьма интересен и тем, что легко устанавливается в любой ноутбук или ультрабук, так как имеет толщину всего 7 мм

Хотя широкое распространение и доступность специализированных сервисов для просмотра потокового видео в интернете в значительной степени подорвали позиции телевидения как основного источника развлекательного и новостного видеоконтента, ТВ-тюнеры еще рано списывать со счетов. Например, эти устройства могут здорово выручить в мобильных условиях, когда скорость интернет-соединения невелика, а трафик слишком дорог. Именно на эту нишу нацелена компактная внешняя модель AVerMedia TD310, о которой пойдет речь в данной публикации

Предлагаем вниманию читателей обзор пяти моделей источников бесперебойного питания (ИБП) мощностью от 1000 до 3000 В•А, которые предназначены для защиты электропитания компьютеров, серверов и коммуникационного оборудования